# High Speed Wallace Tree Multiplier

D. Sai Srinivas<sup>1</sup>, G.Sai Chandu<sup>2</sup>, G.Ajay Kumar<sup>3</sup>, Smithashree Mohapatra<sup>4</sup>

<sup>1, 2, 3</sup> BE Student, Department of Electronics and Communication Engineering, MVSR Engineering College,

Hyderabad, Telangana, India.

<sup>4</sup> Assistant Professor, Department of Electronics and Communication Engineering, MVSR Engineering College, Hyderabad, Telangana, India.

Abstract - Achieving high speed integrated circuits with low power consumption is a major concern for the VLSI circuit designers. Most arithmetic operations are done using multiplier, which is the major power consuming element in the digital circuit. In the present scenario, Fast multipliers with less power consumption are leading with their performance, basically process of multiplication is realized in hardware in terms of shift and add operation. The optimization of adder has led to the improvement in performance of multiplier. In this paper, multiplier is proposed using modified full adder, carry save adder and carry select adder using binary to excess one converter, to bring out the best multiplier with low power and high speed. To analyze the efficiency of proposed design, the conventional Wallace tree multiplier structure is used. The designs are developed using Verilog HDL(vivado) and the functionalities are verified through simulation. Synthesis results of the multiplier shows an average reduction in power, delay compared to the existing approaches.

Index Terms – Wallace tree multiplier, fulladder, carry save adder, carry select adder and binary to excess one converter.

#### 1. INTRODUCTION

The power consumption, delay and area are always been an important design considerations for any chip designer. Many DSP structures incorporate multipliers in their design. Delay of the circuit inevitably changes with the delay of the multiplier. Therefore research is going on to reduce the delay of multiplier so that the delay of whole circuit can be reduced. An early description of the Wallace tree multiplier was given by [1]. Wallace tree multiplier has been evolved as high speed and area efficient multiplier. The Wallace tree multiplier involves ANDing of multiplier and multiplicand bits for the generation of partial products. In second phase full adders and half adders has been used for the reduction of generated partial products in two rows.

Followed by addition of two rows using fast carry adders in the third stage. In recent years a lot of research work has been carried out to reduce the complexity of the multiplier. In [2], the reordering of partial products is employed in such a way so as to reduce the switching activity which leads to reduction in power. Partitioning the partial product tree into four groups and applying Dadda to one group and Wallace multiplier to another and so on also achieves power reduction [3].In [4], a full adder

using 4:1 multiplexers is used in the reduction phase to reduce the power. In [5], full adder is designed using six 2:1 multiplexers. In [6] modified full adder is used in the reduction phase which produces less delay. In [7] multiplier is realized using carry save adder which reduces delay. In [8] multiplier is realized by carry select adder which consumes less power and less delay compared to above mentioned adders.

The rest of the paper is organized as follows: Section II discusses the related works of full adder. Section III presents the architecture of high speed adders. The discussion and results are summarized in section IV and finally section V, concludes the paper.

#### 2. TRADITIONAL WALLACE TREE MULTIPLIER

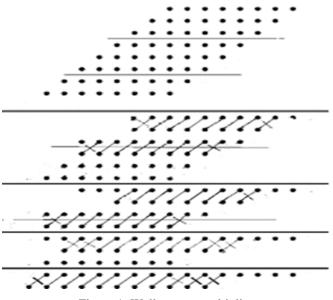

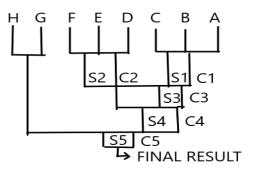

Wallace proposed the column compression technique for fast multiplication operations in which the total delay is proportional to the logarithm of the word length of multiplier operand [1]. The Wallace tree multiplier with column compression technique is faster than array multipliers, because the delay in an array multiplier varies linearly, whereas in Wallace it varies logarithmically. Let us consider a N bits multiplication, N2 AND gates are required in order to generate the partial product terms and the number of reduction stages is given by S which is shown in (1)

## $S = \log 2N(1)$

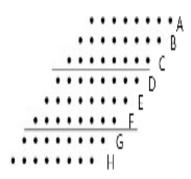

The number of half adders is at least N - 1, and is often much greater than N. Fig. 1 illustrates the reduction tree of 8 x 8 bits unsigned multiplier. Each dot represents a single-bit partial product. Starting from the right most column, when three bits come across, full adders and for two bits, half adders are used respectively. The sum and carry outputs for each adder at one stage are again represented as dots in the next stage and are used as inputs of adders in that stage (or sent directly to the final adder).

Each column has a certain order of magnitude of the partial products. The sum output at one stage reflect a dot in the same column at the next stage. The carry output at one stage reflects a dot in the column to its left i.e. one order of magnitude higher.

Figure 1: Wallace tree multiplier

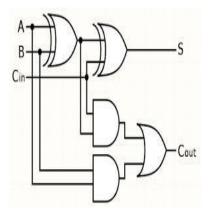

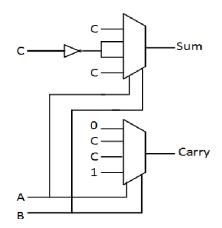

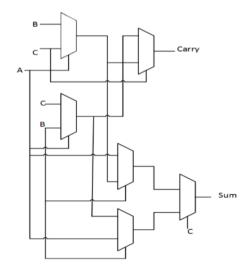

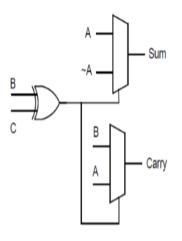

In Wallace tree multiplier full adder is proposed in four different formats which is shown below figures.

Figure2: conventional full adder

Figure3: full adder using 4:1 mux

Figure 4: full adder using six 2:1 mux

Figure 5:modified full adder

Table-1: Comparison of area, power and delay

| Multiplier                         | Area(LUT'S) | Power(watts) | Delay(nS) |

|------------------------------------|-------------|--------------|-----------|

| Conventional full adder            | 79          | 4.6          | 15.219    |

| MUX Based<br>full adder            | 81          | 4.707        | 15.599    |

| Full adder<br>using six 2:1<br>mux | 81          | 4.677        | 14.899    |

| Modified full<br>adder             | 104         | 5.3          | 14.659    |

## International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 6, Issue 3, March (2018) www.ijeter.everscience.org

The above table shows the synthesis results of Wallace tree multiplier using different types of full adders. From the above table it is clear that multiplier being realized by modified full adder is the fastest circuit that has less propagation delay but it is consuming more power. In order to reduce the power we have implemented the multiplier using high speed adders which were discussed in section-III.

#### 3. HIGH SPEED ADDERS

## 3.1 Carry save adder

Using carry save addition, the delay can be reduced further still. The idea is to take 3 numbers that we want to add together, x +y + z, and convert it into 2 numbers c + s such that x + y + z =c + s. Another way to look at it is that any carry over from one column gets put into the next column. Now, we can add together c and s, The important point is that c and s can be computed independently, and furthermore, each carry input (and sum input) can be computed independently from obtained partial products. This achieves our original goal of converting three numbers that we wish to add into two numbers that add up to the same sum, It is actually identical to the full adder, but with some of the signals renamed. Figure 6 shows a full adder and a carry save adder. A carry save adder simply is a full adder with the cin input renamed to z, the z output (the original "answer" output) renamed to s, and the cout output renamed to c.

| x:   |   |   | 1 | 0 | 0 | 1 | 1 |  |

|------|---|---|---|---|---|---|---|--|

| y:   |   |   | 1 | 1 | 0 | 0 | 1 |  |

| z:   | + |   | 0 | 1 | 0 | 1 | 1 |  |

| s:   |   |   | 0 | 0 | 0 | 0 | 1 |  |

| c:   | + | 1 | 1 | 0 | 1 | 1 |   |  |

| sum: |   | 1 | 1 | 0 | 1 | 1 | 1 |  |

Figure 6.1: carry save adder

| У | :        | 1 | 1 | 0 | 0 | 1 |   |

|---|----------|---|---|---|---|---|---|

|   | :<br>: 1 |   |   |   |   | 1 | — |

Figure 6.2: full adder

In the Wallace tree multiplier carry save adder logic goes this way, name all the partial product columns as A,B,C,...H and add according to block diagram.

Figure 7: Block diagram of wallace multiplier using csa

Figure 8: Carry save adder

Table-2: Comparison of Area, delay and delay

| Multiplier          | Area(LUT'S) | Power(watts) | Delay(nS) |

|---------------------|-------------|--------------|-----------|

| Carry save<br>adder | 100         | 5.3          | 14.1      |

3.2 Carry select adder (BEC)

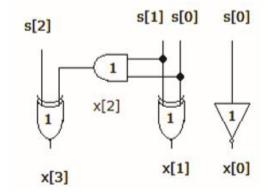

Wallace tree multiplier is designed with CSLA in order to increase the speed. This gives the solution for the problem of carry propagation delay by independently generating multiple carries and then selects a carry to obtain the sum. As we know CSLA is not area efficient as it uses multiple pairs of Ripple Carry Adders(RCA) partial sum and carry by considering cin=0 and cin =1,then final sum and carry are selected by multiplexers, this disadvantage made a reason to replace RCA in regular CSLA with binary to excess-1 converter(BEC).

BEC is replaced instead of RCA with cin = 1 in regular CSLA to achieve the lower area, power consumption and uses less number of logic gates, then final sum and carry is selected through MUX[9]. The importance of BEC logic stems from the large silicon area reduction when the CSLA with large number of bits are designed. In regular CLSA as the utilization of gates are more due to this power consumption also increases. Now by using BEC in regular CSLA we can reduce number of gates and simultaneously decreases power consumption [10]-[12].

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 6, Issue 3, March (2018) www.ijeter.everscience.org

a0b7 a0b6 a0b5 a0b4 a0b3 a0b2 a0b1 a0b0 a1b7 a1b6 a1b5 a1b4 a1b3 a1b2 a1b1 a1b0

a2b7 a2b6 a2b5 a2b4 a2b3 a2b2 a2b1 a2b0

a3b7 a3b6 a3b5 a3b4 a3b3 a3b2 a3b1 a3b0

a4b7 a4b6 a4b5 a4b4 a4b3 a4b2 a4b1 a4b0

a5b7 a5b6 a5b5 a5b4 a5b3 a5b2 a5b1 a5b0

a6b7 a6b6 a6b5 a6b4 a6b3 a6b2 a6b1 a6b0 a7b7 a7b6 a7b5 a7b4 a7b3 a7b2 a7b1 a7b0

Figure9: Block diagram of Wallace partial products

a0b7 a0b6 a0b5 a0b4 a0b3 a0b2 a0b1 a0b0 a1b7 a1b6 a1b5 a1b4 a1b3 a1b2 a1b1 a1b0 a2b7 a2b6 a2b5 a2b4 a2b3 a2b2 a2b1 a2b0

| a2b7 | s7 | s6 | s5 | s4 | s3 | s2 | s1 | s0 | a0b0 |

|------|----|----|----|----|----|----|----|----|------|

| c7   | с6 | c5 | c4 | c3 | c2 | c1 | c0 |    |      |

Figure10: First stage

a3b7 a3b6 a3b5 a3b4 a3b3 a3b2 a3b1 a3b0 a4b7 a4b6 a4b5 a4b4 a4b3 a4b2 a4b1 a4b0 a5b7 a5b6 a5b5 a5b4 a5b3 a5b2 a5b1 a5b0

| a5b7 | s15 | s14 | s13 | s12 | s11 | s10 | s9 | s8 | a3b0 |

|------|-----|-----|-----|-----|-----|-----|----|----|------|

| c15  | c14 | c13 | c12 | c11 | c10 | c9  | c8 |    |      |

Figure11: second stage

|      |     |     | a2b7 | s7  | s6  | s5  | s4 | s3 | s2   | s1 | s0 | a0b0 |  |

|------|-----|-----|------|-----|-----|-----|----|----|------|----|----|------|--|

|      |     |     | c7   | сб  | c5  | c4  | c3 | c2 | c1   | c0 |    |      |  |

| a5b7 | s15 | s14 | s13  | s12 | s11 | s10 | s9 | s8 | a3b0 |    |    |      |  |

a5b7 s15 s14 s23 s22 s21 s20 s19 s18 s17 s16 s0 a0b0 c23 c22 c21 c20 c19 c18 c17 c16

## Figure12: Third stage

c15 c14 c13 c12 c11 c10 c9 c8 a6b7 a6b6 a6b5 a6b4 a6b3 a6b2 a6b1 a6b0 a7b7 a7b6 a7b5 a7b4 a7b3 a7b2 a7b1 a7b0

a7b7 s31 s30 s29 s28 s27 s26 s25 s24 c8 c31 c30 c29 c28 c27 c26 c25 c24

Figure13: fourth stage

a5b7 s15 s14 s23 s22 s21 s20 s19 s18 s17 s16 s0 a0b0 c23 c22 c21 c20 c19 c18 c17 c16 a7b7 s31 s30 s29 s28 s27 s26 s25 s24 c8

a7b7 s41 s40 s39 s38 s37 s36 s35 s34 s33 s32 s16 s0 a0b0 c41 c40 c39 c38 c37 c36 c35 c34 c33 c32

Figure14: Fifth stage

a7b7 s31 s41 s40 s39 s38 s37 s36 s35 s34 s33 s32 s16 s0 a0b0 c41 c40 c39 c38 c37 c36 c35 c34 c33 c32 c31 c30 c29 c28 c27 c26 c25 c24

s52 s51 s50 s49 s48 s47 s46 s45 s44 s43 s42 s33 s32 s16 s0 a0b0 c52 c51 c50 c49 c48 c47 c46 c45 c44 c43 c42

# Figure15: sixth stage

s52

s51

s50

s49

s48

s47

s46

s45

s44

s43

s42

s33

s32

s16

s0

a0b0

c52

c51

c50

c49

c48

c47

c46

c45

c44

c43

c42

c62

c61

c60

c59

c58

c57

c56

c55

c54

1'b 0

s63 s62 s61 s60 s59 s58 c57 s56 s55 s54 s53 s42 s33 s32 s16 s0 a0b0

## Figure16: Seventh stage

Results of sum [64-73] with c53=1 can be obtained by passing s[54-63] to binary to excess one convertor(BEC) as inputs. A sample of BEC is illustrated in Fig:17. Depending on the value of c53 either output of s[54-63] or output of s[64-73] will be chosen by multiplexer(MUX) as shown in Fig-18.

Two bit BEC

Figure 17: BEC with partial products as inputs

Figure18: multiplexers circuit

#### 4. SYNTHESIS RESULTS

Table-3: Comparison of area, power and delay

| Multiplier<br>using               | Area(LUT's) | Power(watts) | Delay(nsec) |

|-----------------------------------|-------------|--------------|-------------|

| 8                                 |             |              |             |

| Modified<br>fulladder             | 104         | 5.3          | 14.6        |

| Carry save<br>adder               | 100         | 5.3          | 14.1        |

| Carry select<br>adder with<br>BEC | 100         | 3.8          | 12.6        |

The table shows the Synthesis results of Wallace Tree Multiplier using different adders. From the table it is clear that wallace tree multiplier when implemented using carry select adder there is reduction in power by 28.3% and delay got reduced by 13% compared to full adder and carry save adders.

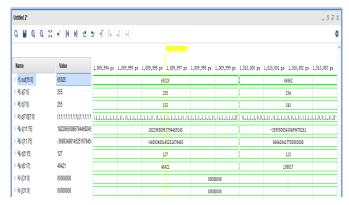

Simulation results

Intitled 2t

| Name            | Value                        | 1,008 ns          | 1,010 ns     | 1,012 ns        | 1,014 ns  | : 1,016 ns         | 1,018 ns       |

|-----------------|------------------------------|-------------------|--------------|-----------------|-----------|--------------------|----------------|

| > 📲 a[7:0]      | 45                           | 153               | X            | 15              |           | 45                 | 1              |

| > 鞜 b[7:0]      | 82                           | 158               | X            | 15              |           | 82                 |                |

| > 📲 out[15:0]   | 3690                         | 24174             | X            | 225             |           | 3690               |                |

| > 💐 p[7:0][7:0] | (0,0,0,0,0,0,0,0),(0,0,1,0,1 | (1,0,),1,1,0,0,1) | (0,0,0,0,0,0 | 0,0,0),(0,0,0,0 | ,0,0,00 ) | (0,0,0,0,0,0,0,0), | (0,0,1,0,1,1,0 |

| > 💐 s[0:55]     | 40267526216589248            | 71782986739545929 | 248          | 39041144848384  |           | 40267526216        | 3539248        |

| > 💐 d[0:55]     | 141291572953088              | 149814939551872   | 719-         | 43519706546176  |           | 1412915725         | 353088         |

| > 🐳 i(31:0)     | 8                            |                   |              | 8               |           |                    |                |

| > 💐 j[31:0]     | 8                            |                   |              | 8               | -         |                    |                |

Figure19: Modified full adder simulation result

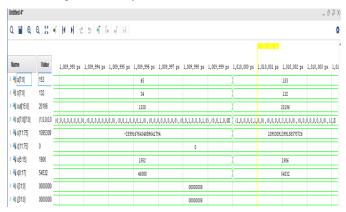

The Simulation results are carried out for wallace tree multiplier using various adders. The performance evaluation of

Wallace Tree multiplier using modified full adder, carry save adder, carry select adder with BEC is carried out using Xilinx Vivado design suite 2017.4.

Figure20: Carry save adder simulation result

Figure21: Carry select adder with BEC

#### 5. CONCLUSION

A Simple approach is proposed in this paper to reduce the power consumption of Wallace tree multiplier using CSLA. From the above results it is observed that the Wallace tree multiplier using CSLA with BEC is consuming less power, occupying less area when compared to Wallace tree multiplier using full adders and carry save adders.

#### REFERENCES

- C. Wallace, "A suggestion for a fast multiplier," IEEE Transaction onElectronic Computers, Vol. EC-13, pp.14-17.

- [2] M. V. P. Kumar, S. Sivanantham, S. Balamurugan, P. S. Mallick, "Low power reconfigurable multiplier with reordering of partial products," in International Conference on Signal Processing, Communication, Computing and Networking Technologies (ICSCCN), Thuckafay, 21-22 July 2011, pp.532-536.

- [3] P. Anitha, P. Ramanathan, "A new hybrid multiplier using Dadda and Wallace method," in International Conference on Electronics and Communication Systems (ICECS), Coimbatore, India, 13-14 Feb. 2014, pp.1-4.

- [4] S. Murugeswari, S. K. Mohideen, "Design of area efficient and low power multipliers using multiplexer based full adder," in 2nd

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 6, Issue 3, March (2018) www.ijeter.everscience.org

International Conference on Current Trends in Engineering and technology (ICCTET), Enathi, India, July 2014, pp.388-392.

- [5] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "A Novel Multiplexer-Based Low-Power Full Adder," IEEE transactions on circuits and systems, vol. 51, no. 7, July 2004, pp. 345-348.

- [6] Kokila Bharti Jaiswal1, Nithish Kumar V1, Pavithra Seshadri2 and Lakshminarayanan G "Low Power Wallace Tree Multiplier Using Modified Full Adder", International Conference on Signal Processing, Communication and Networking (ICSCN).

- [7] Introduction to VLSI Circuits and Systems by John P.Uyemera.

- [8] R. Bala Sai Kesava, K. BalaSindhuri , B. Lingeswararao , N. Udaya Kumar "Low Power And Area Efficient Wallace Tree Multiplier Using Carry Select Adder With Binary To Excess-1 Converter" Conference on Advances in Signal Processing (CASP) Cummins College of Engineering for Women, Pune. Jun 9-11, 2016.

- [9] Naveen Kr. Gahlan ,Prabhat Shukla,Jasbir Kaur, "Implementation of Wallace Tree Multiplier Using Compressor", NaveenKr.Gahlan et al ,Int.J.Computer Technology & Applications, Vol 3 (3), 1194-1199.

- [10] B.Ramkumar and Harish M Kittur "Low-Power and Area-Efficient Carry Select Adder"371-375, VOL. 20, NO. 2, FEBRUARY 2012.

- [11] K.Gopi Krishna, B.Santhosh, V.Sridhar, "Design of WallaceTree Multiplier using Compressors", International Journal ofEngineering Sciences & Research Technology. ISSN: 2277-9655. September 2013.

- [12] E. Prakash, R. Raju, Dr.R. Varatharajan, "Effective Method ForImplementation of Wallace Tree using Fast Adders", Journal ofInnovativeResearch and Solutions (JIRAS), Volume. 1, IssueNo. 1, July –Dec 2013.

Authors

Devana Sai Srinivas, is an B.E Student (Electronics and Communication Engineering)In MVSR Engineering College.

Gali Sai Chandu,, is an B.E Student(Electronics and communication Engineering) In MVSR Engineering College.

Gunji Ajay Kumar, is an B.E Student (Electronics and communication Engineering) In MVSR Engineering College.

SmithaShree Mohapatra is an Assistant Professor at MVSR Engineering College, Hyderabad in ECE Department,She has received here B.Tech degree in Electronics and Communication Engineering and M.Tech degree in VLSI design. Here main research interest are VLSI design and analysis, digital VLSI, digital Electronics and low power VLSI